软件介绍

Synopsys Synplify是一款专业的FPGA设计软件,在软件中集成了FPGA综合设计环境,让用户能够使用软件快速高效的进行开发处理。软件中有着丰富的功能帮助用户进行设计,对于专业的人员来说能够极大的提升工作效率,软件专业性较强,适合专业人士进行使用。

软件功能

增量的、基于块的和自下而上的流程,从一次运行到下一次运行保持一致的结果

自动编译点增量流可将运行时间提高 4 倍,同时保持 QoR

支持多达 4 个处理器的加速运行时间

脚本和 Tcl/Find 支持流程自动化和可定制的综合、调试和报告

使用来自 Achronix、Altera、Lattice、Microsemi、Xilinx 的 FPGA 的最佳面积和时序结果

分层团队设计流程允许并行和/或地理分布的设计开发

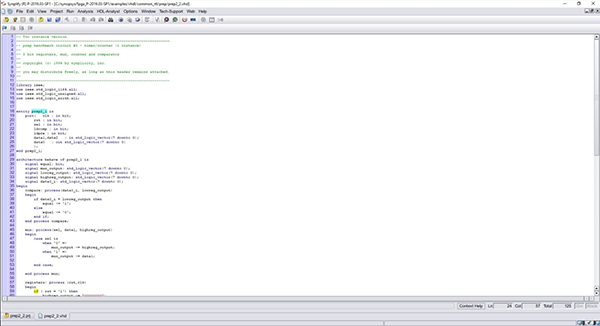

全面的语言支持,包括 Verilog、VHDL、SystemVerilog、VHDL-2008 和混合语言设计

FSM Compiler 和 FSM Explorer,用于从 RTL 中自动提取和优化有限状态机

图形状态机查看器可自动创建气泡图以调试和记录 FSM

自动存储器和 DSP 推理提供具有最佳面积、功率和时序质量结果的设计的自动实施

用于分析的增量静态时序允许更新时序异常约束,立即查看结果,无需重新综合

HDL Analyst 交互式图形分析和调试工具,用于设计诊断、问题隔离以及功能和性能分析

软件特色

1、快速的运行时间和增量功能,可在最快的时间内实现结果

2、最好的质量结果(结果质量)的性能调度的行业

3、逻辑到最小化的降低的成本和功率

4、提供多个目标的FPGA从一个单一RTL源

5、HDL分析仪原理观众对于快速调试和调整限制

6、通过比较FSM性能和来自ECC存储器的推断来减少SEU(包括重复TMR)的自动化

7、支持第三方FPGA

8、能力到调试操作FPGA直接在RTL代码

9、整合与Synphony模型编译器的实现算法的DSP

10、分析工具,以降低动态功耗消耗

11、支持基于原型的FPGA,包括门和时钟转换生成

12、支持的块建筑Synopsys的DesignWare的和的DesignWare核心的的数字,以确保兼容性ASIC当前

13、该设计为发展的分布和平行与流顶部至底部/自下而上或组合

14、自动化和定制,包括Tcl手和查找流

网友评论